# DCR4880M42

# **Phase Control Thyristor**

DS5943-5 February 2019 (LN37316)

#### **FEATURES**

- Double Side Cooling

- High Surge Capability

#### **APPLICATIONS**

- High Power Drives

- High Voltage Power Supplies

- Static Switches

#### **VOLTAGE RATINGS**

| Part and<br>Ordering<br>Number          | Repetitive Peak<br>Voltages<br>V <sub>DRM</sub> and V <sub>RRM</sub><br>V | Conditions                                                                                                                                                                                                                               |

|-----------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCR4880M42*<br>DCR4880M40<br>DCR4880M35 | 4200<br>4000<br>3500                                                      | $\begin{split} T_{vj} = -40^{\circ}\text{C to } 125^{\circ}\text{C}, \\ I_{DRM} = I_{RRM} = 300\text{mA}, \\ V_{DRM}, V_{RRM}  t_p = 10\text{ms}, \\ V_{DSM}  \&  V_{RSM} = \\ V_{DRM}  \&   V_{RRM} + 100V \\ respectively \end{split}$ |

Lower voltage grades available. \*4100V @ -40°C, 4200V @ 0°C

### **ORDERING INFORMATION**

When ordering, select the required part number shown in the Voltage Ratings selection table.

For example:

#### DCR4880M42

Note: Please use the complete part number when ordering and quote this number in any future correspondence relating to your order.

#### **KEY PARAMETERS**

$\begin{array}{lll} V_{DRM} & 4200V \\ I_{T(AV)} & 4880A \\ I_{TSM} & 60800A \\ dV/dt^* & 2000V/\mu s \\ dI/dt & 400A/\mu s \end{array}$

#### \* Higher dV/dt selections available

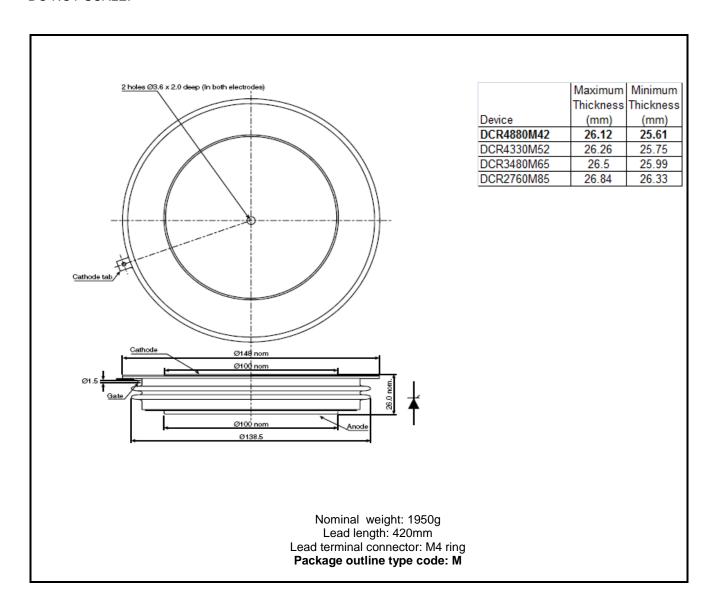

Fig. 1 Package outline

### **CURRENT RATINGS**

### $T_{case} = 60$ °C unless stated otherwise

| Symbol              | Parameter                            | Test Conditions          | Max. | Units |

|---------------------|--------------------------------------|--------------------------|------|-------|

| Double Si           | de Cooled                            |                          |      |       |

| I <sub>T(AV)</sub>  | Mean on-state current                | Half wave resistive load | 4880 | А     |

| I <sub>T(RMS)</sub> | RMS value                            | -                        | 7665 | А     |

| I <sub>T</sub>      | Continuous (direct) on-state current | -                        | 7020 | А     |

### **SURGE RATINGS**

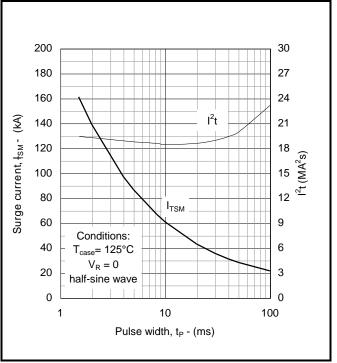

| Symbol           | Parameter                               | Test Conditions                           | Max.  | Units             |

|------------------|-----------------------------------------|-------------------------------------------|-------|-------------------|

| I <sub>TSM</sub> | Surge (non-repetitive) on-state current | 10ms half sine, T <sub>case</sub> = 125°C | 60.8  | kA                |

| l <sup>2</sup> t | I <sup>2</sup> t for fusing             | $V_R = 0$                                 | 18.48 | MA <sup>2</sup> s |

### THERMAL AND MECHANICAL RATINGS

| Symbol               | Parameter                             | Test Conditions                             |             | Min. | Max.    | Units |

|----------------------|---------------------------------------|---------------------------------------------|-------------|------|---------|-------|

| R <sub>th(j-c)</sub> | Thermal resistance – junction to case | Double side cooled                          | DC          | -    | 0.00518 | °C/W  |

|                      |                                       | Single side cooled                          | Anode DC    | -    | 0.01012 | °C/W  |

|                      |                                       |                                             | Cathode DC  | -    | 0.01080 | °C/W  |

| R <sub>th(c-h)</sub> | Thermal resistance – case to heatsink | Clamping force 83.0kN                       | Double side | -    | 0.001   | °C/W  |

|                      |                                       | (with mounting compound)                    | Single side | -    | 0.002   | °C/W  |

| $T_{vj}$             | Virtual junction temperature          | Blocking V <sub>DRM</sub> / <sub>VRRM</sub> |             | -    | 125     | °C    |

| T <sub>stg</sub>     | Storage temperature range             |                                             |             | -55  | 125     | °C    |

| F <sub>m</sub>       | Clamping force                        |                                             |             | 74.0 | 91.0    | kN    |

# **DYNAMIC CHARACTERISTICS**

| Symbol                             | Parameter                                     | Test Conditions                                                                                                       |                 | Min. | Max.  | Units |

|------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------|------|-------|-------|

| I <sub>RRM</sub> /I <sub>DRM</sub> | Peak reverse and off-state current            | At V <sub>RRM</sub> /V <sub>DRM</sub> , T <sub>case</sub> = 125°C                                                     |                 | -    | 300   | mA    |

| dV/dt                              | Max. linear rate of rise of off-state voltage | To 67% V <sub>DRM</sub> , T <sub>j</sub> = 125°C, ga                                                                  | ate open        | -    | 2000  | V/µs  |

| dl/dt                              | Rate of rise of on-state current              | From 67% V <sub>DRM</sub> to 2x I <sub>T(AV)</sub>                                                                    | Repetitive 50Hz | -    | 200   | A/µs  |

|                                    |                                               | Gate source 30V, 10Ω,                                                                                                 | Non-repetitive  | -    | 500   | A/µs  |

|                                    |                                               | $t_r < 0.5 \mu s, T_j = 125^{\circ}C$                                                                                 |                 |      |       |       |

| $V_{T(TO)}$                        | Threshold voltage – Low level                 | 500 to 2200A at T <sub>case</sub> = 125°                                                                              | С               | -    | 0.75  | V     |

|                                    | Threshold voltage – High level                | 2200 to 8000A at T <sub>case</sub> = 125                                                                              | °C              | -    | 0.92  | V     |

| r <sub>T</sub>                     | On-state slope resistance – Low level         | 500 to 2200A at T <sub>case</sub> = 125°                                                                              | С               | -    | 0.205 | mΩ    |

|                                    | On-state slope resistance – High level        | 2200 to 8000A at T <sub>case</sub> = 125°C                                                                            |                 | -    | 0.122 | mΩ    |

| t <sub>gd</sub>                    | Delay time                                    | $V_D = 67\% V_{DRM}$ , gate source 30V, $10\Omega$                                                                    |                 | -    | 3     | μs    |

|                                    |                                               | $t_r = 0.5 \mu s, T_j = 25^{\circ}C$                                                                                  |                 |      |       |       |

| tq                                 | Turn-off time                                 | $T_j$ = 125°C, 5000A<br>$V_R$ = 200V, dl/dt = 5 A/ $\mu$ s,                                                           |                 |      | 900   | μs    |

|                                    |                                               | dV <sub>DR</sub> /dt = 20V/μs linear                                                                                  |                 |      |       |       |

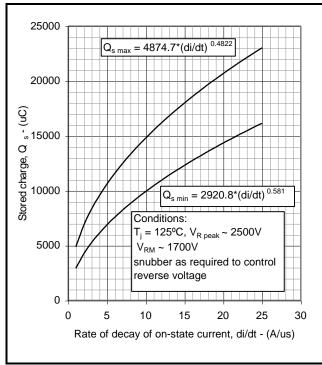

| Qs                                 | Stored charge                                 | - I <sub>T</sub> = 3000A, T <sub>j</sub> = 125°C, dI/dt – 1A/μs,<br>V <sub>Rpeak</sub> ~3100V, V <sub>R</sub> ~ 2100V |                 | 2920 | 4875  | μC    |

| I <sub>RR</sub>                    | Reverse recovery current                      |                                                                                                                       |                 | 42   | 57    | А     |

| IL                                 | Latching current                              | $T_j = 25$ °C, $V_D = 5V$                                                                                             |                 | -    | 3     | А     |

| I <sub>H</sub>                     | Holding current                               | $T_j = 25$ °C, $R_{G-K} = \infty$ , $I_{TM} = 500$ A, $I_T = 5$ A                                                     |                 | -    | 300   | mA    |

### **GATE TRIGGER CHARACTERISTICS AND RATINGS**

| Symbol          | Parameter                | Test Conditions                                     | Max. | Units |

|-----------------|--------------------------|-----------------------------------------------------|------|-------|

| $V_{GT}$        | Gate trigger voltage     | $V_{DRM} = 5V$ , $T_{case} = 25$ °C                 | 1.5  | V     |

| $V_{GD}$        | Gate non-trigger voltage | At 50% V <sub>DRM</sub> , T <sub>case</sub> = 125°C | 0.4  | V     |

| I <sub>GT</sub> | Gate trigger current     | $V_{DRM} = 5V$ , $T_{case} = 25$ °C                 | 400  | mA    |

| $I_{GD}$        | Gate non-trigger current | At 50% V <sub>DRM</sub> , T <sub>case</sub> = 125°C | 10   | mA    |

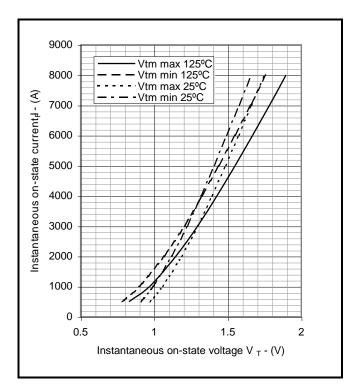

#### **CURVES**

Fig.2 Maximum & minimum on-state characteristics

**V<sub>TM</sub> EQUATION**

$V_{TM} = A + BIn (I_T) + C.I_T + D.\sqrt{I_T}$

Where A = -0.208640

B = 0.171688

C = 0.000113

D = - 0.003842

these values are valid for  $T_j = 125$ °C for  $I_T 500$ A to 8000A

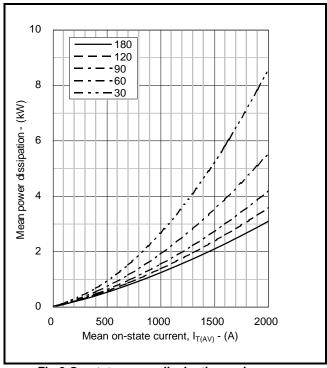

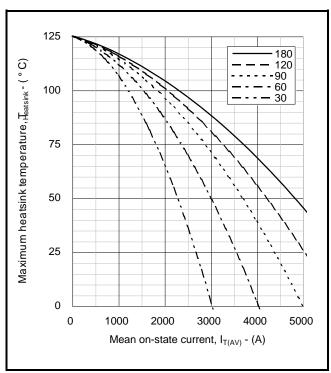

Fig.3 On-state power dissipation - sine wave

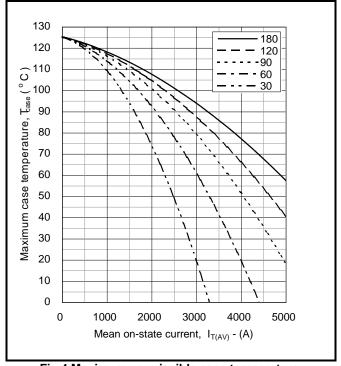

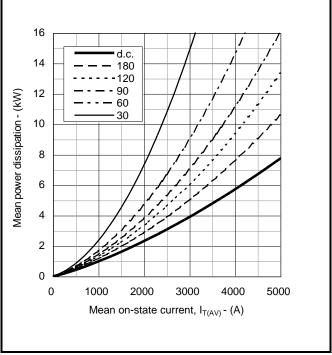

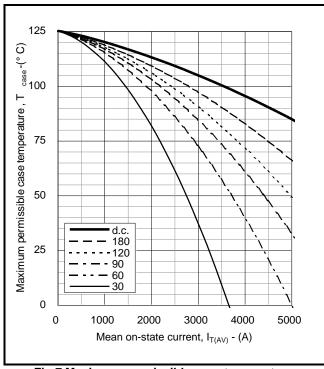

Fig.4 Maximum permissible case temperature, double side cooled – sine wave

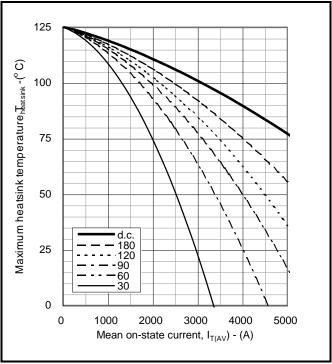

Fig.5 Maximum permissible heatsink temperature, double side cooled – sine wave

Fig.6 On-state power dissipation - rectangular wave

Fig.7 Maximum permissible case temperature, double side cooled – rectangular wave

Fig.8 Maximum permissible heatsink temperature, double side cooled – rectangular wave

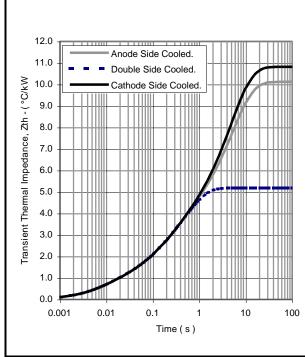

|                      |                        | 1        | 2        | 3        | 4        |

|----------------------|------------------------|----------|----------|----------|----------|

| Double side cooled   | R <sub>i</sub> (°C/kW) | 1.995338 | 1.242784 | 1.9448   | 0.005    |

| Double side cooled   | T <sub>i</sub> (s)     | 0.05     | 0.592935 | 0.592385 | 110.5108 |

| Anode side cooled    | R <sub>i</sub> (°C/kW) | 6.092995 | 1.957372 | 2.042252 | 0.035908 |

| Ariode side cooled   | T <sub>i</sub> (s)     | 5.459764 | 0.510898 | 0.05     | 110.1735 |

| Cathode side cooled  | R <sub>i</sub> (°C/kW) | 6.856845 | 1.876401 | 2.062845 | 0.025343 |

| Catrioue side cooled | T: (s)                 | 5.181139 | 0.557321 | 0.05     | 110.1546 |

$$Z_{th} = \sum_{i=1}^{i=4} [R_i \times (1 - \exp(T/T_i))]$$

# $\Delta R_{th(j-c)}$ Conduction

Tables show the increments of thermal resistance  $R_{\text{th(j-c)}}$  when the device operates at conduction angles other than d.c.

| Double side cooling |                     |       |  |  |

|---------------------|---------------------|-------|--|--|

|                     | $\Delta Z_{th}$ (z) |       |  |  |

| θ°                  | sine.               | rect. |  |  |

| 180                 | 0.51                | 0.36  |  |  |

| 120                 | 0.57                | 0.49  |  |  |

| 90                  | 0.64                | 0.56  |  |  |

| 60                  | 0.70                | 0.63  |  |  |

| 30                  | 0.74                | 0.71  |  |  |

| 15                  | 0.76                | 0.74  |  |  |

| Anode Side Cooling |                     |       |  |  |

|--------------------|---------------------|-------|--|--|

|                    | $\Delta Z_{th}$ (z) |       |  |  |

| θ°                 | sine.               | rect. |  |  |

| 180                | 0.51                | 0.36  |  |  |

| 120                | 0.58                | 0.50  |  |  |

| 90                 | 0.65                | 0.57  |  |  |

| 60                 | 0.71                | 0.64  |  |  |

| 30                 | 0.75                | 0.71  |  |  |

| 15                 | 0.77                | 0.75  |  |  |

| Cathode Sided Cooling |                    |       |  |

|-----------------------|--------------------|-------|--|

|                       | $\Delta Z_{th}(z)$ |       |  |

| θ°                    | sine.              | rect. |  |

| 180                   | 0.51               | 0.36  |  |

| 120                   | 0.58               | 0.50  |  |

| 90                    | 0.65               | 0.57  |  |

| 60                    | 0.71               | 0.64  |  |

| 30                    | 0.75               | 0.71  |  |

| 4.5                   | 0.77               | 0.75  |  |

Fig.9 Maximum (limit) transient thermal impedance - junction to case (°C/kW)

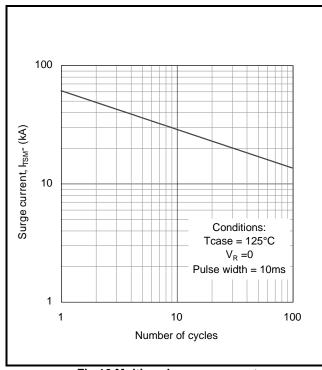

Fig.10 Multi-cycle surge current

Fig.11 Single-cycle surge current

Fig.12 Stored charge

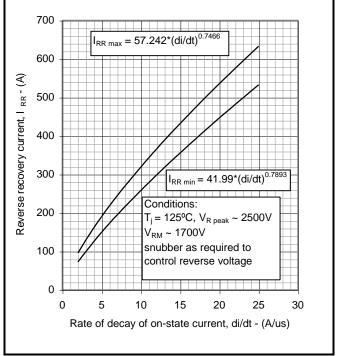

Fig.13 Reverse recovery current

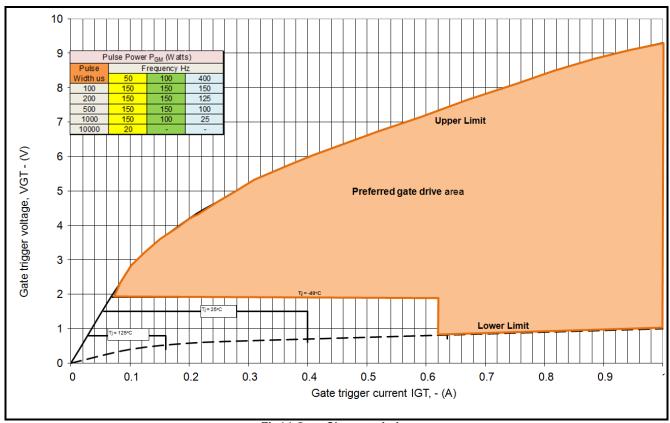

Fig14 Gate Characteristics

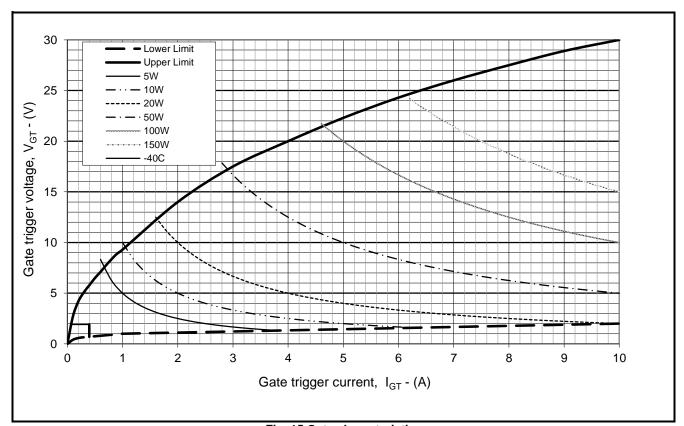

Fig. 15 Gate characteristics

### **PACKAGE DETAILS**

For further package information, please contact Customer Services. All dimensions in mm, unless stated otherwise. DO NOT SCALE.

Fig.16 Package outline

#### IMPORTANT INFORMATION:

The products and data in this publication are intended for use by appropriately trained technical personnel.

Due to the diversity of product applications, the information contained herein is provided as a guide only and does not constitute any guarantee of suitability for use in a specific application. The user must evaluate the suitability of the product and the completeness of the product data for the application. The user is responsible for product selection and ensuring all safety and any warning requirements are met. Should additional product information be needed please contact Customer Service.

This publication is an uncontrolled document and is subject to change without notice. When referring to it, please ensure that it is the most up to date version and has not been superseded.

The products are not intended for use in applications where a failure or malfunction may cause loss of life, injury or damage to property. The user must ensure that appropriate safety precautions are taken to prevent or mitigate the consequences of a product failure or malfunction.

The products must not be touched when operating because there is a danger of electrocution or severe burning. Always use protective safety equipment such as appropriate shields for the product and wear safety glasses. Even when disconnected any electric charge remaining in the product must be discharged and allowed to cool before safe handling using protective gloves.

Extended exposure outside the product ratings may affect reliability leading to premature product failure. Use outside the product ratings is likely to cause permanent damage to the product. In extreme conditions, as with all semiconductors, this may include potentially hazardous rupture, a large current to flow or high voltage arcing, resulting in fire or explosion. Appropriate application design and safety precautions should always be followed to protect persons and property.

#### **Product Status & Product Ordering:**

We annotate datasheets in the top right hand corner of the front page, to indicate product status if it is not yet fully approved for production. The annotations are as follows:-

**Target Information:** This is the most tentative form of information and represents a very preliminary specification. No actual design work on the product has been started.

**Preliminary Information:** The product design is complete and final characterisation for volume production is in progress. The datasheet represents the product as it is now understood but details may change.

No Annotation: The product has been approved for production and unless otherwise notified by Dynex any product ordered will be supplied to the current version of the data sheet prevailing at the time of our order acknowledgement.

All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

All brand names and product names used in this publication are trademarks, registered trademarks or trade names of their respective owners.

#### **HEADQUARTERS OPERATIONS**

DYNEX SEMICONDUCTOR LIMITED Doddington Road, Lincoln, Lincolnshire, LN6 3LF United Kingdom.

Phone: +44 (0) 1522 500500 Fax: +44 (0) 1522 500550 Web: http://www.dynexsemi.com

## **CUSTOMER SERVICE**

Phone: +44 (0) 1522 502753 / 502901 Fax: +44 (0) 1522 500020

e-mail: power\_solutions@dynexsemi.com

© Dynex Semiconductor Ltd. Technical Documentation – Not for resale.